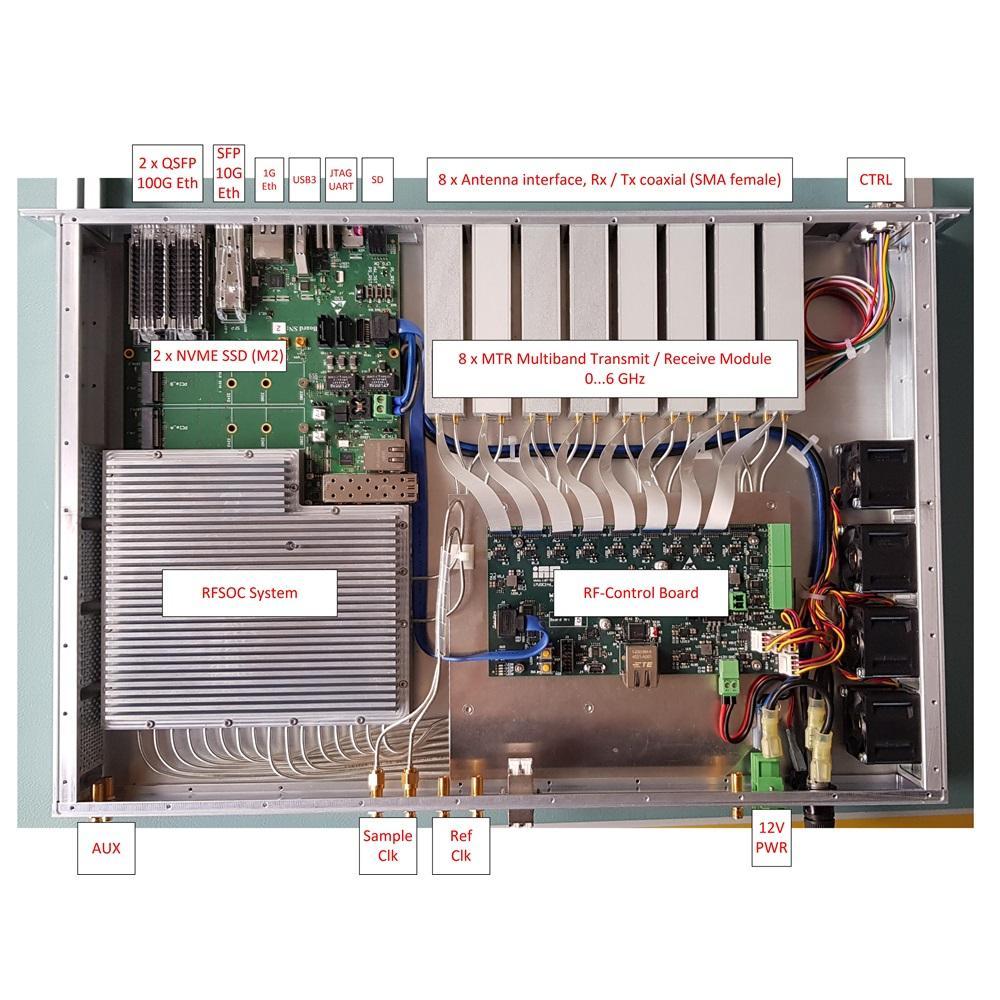

8 Channel Wideband SDR Transceiver with integrated RF frontend up to 6 GHz

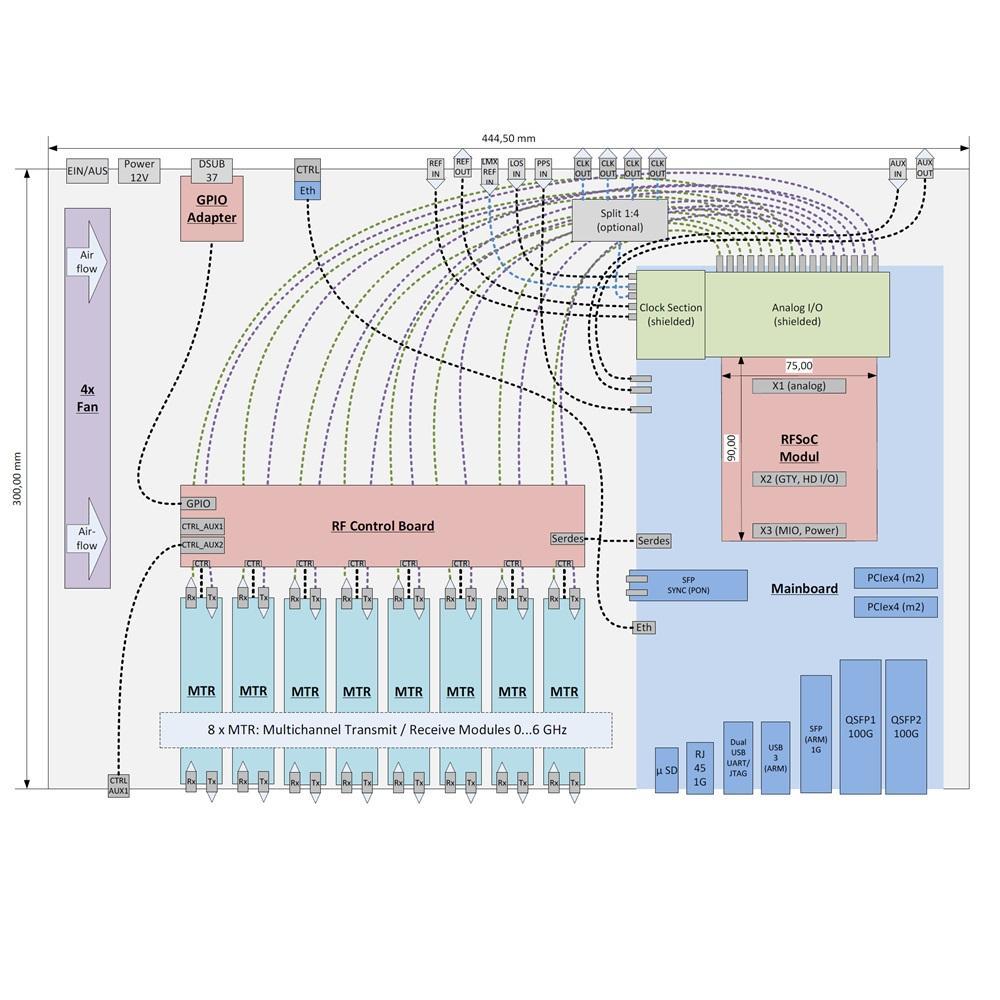

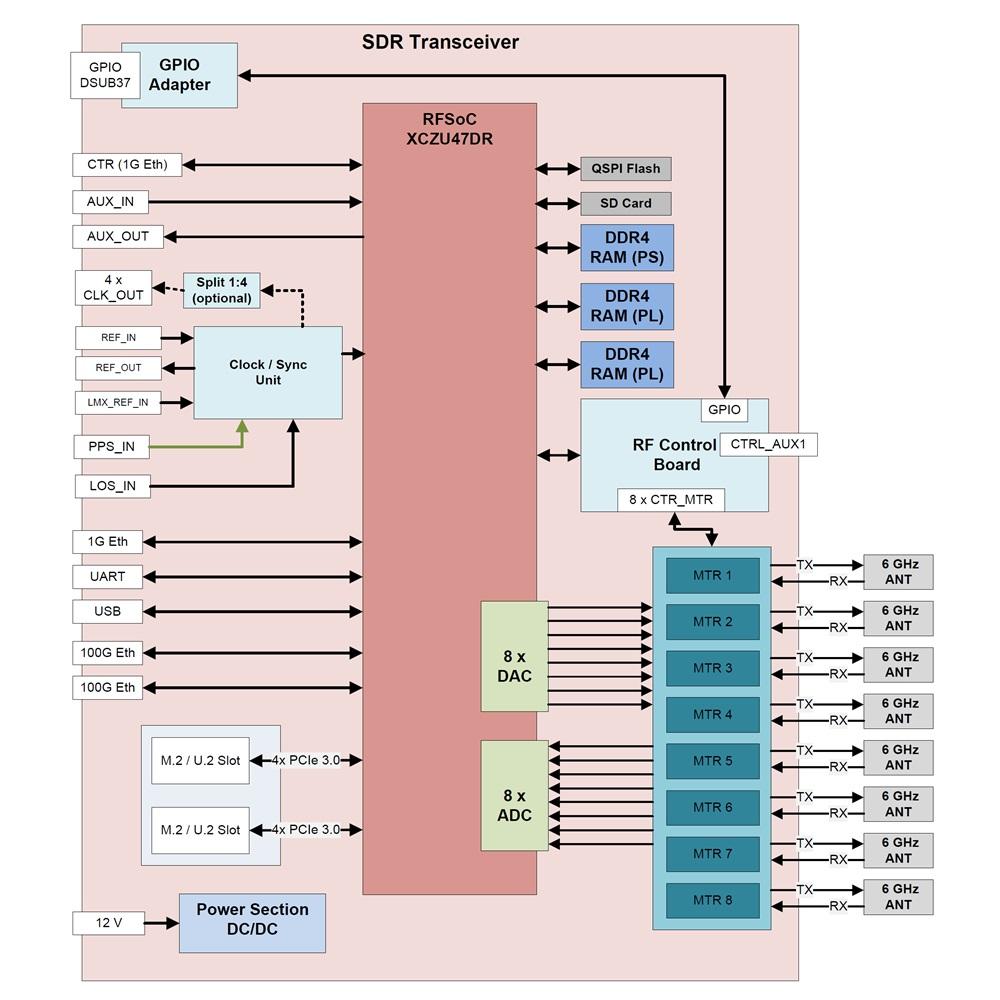

The SDR6004 is an 8-channel wideband SDR transceiver with integrated RF front end up to 6 GHz. The digital baseband signal processing hardware has a modular structure. The RFSoC module on the mainboard includes all digital and analogue interfaces. The RF control board is a separate board for configuration and control of the RF front end modules. The mainboard serves as a carrier for accommodating the RFSoC module and for processing/distributing the RFSoC interface signals. It also contains the global clock section, the generation of the required operating voltages and the PCIe x4 Gen.3 interfaces for connecting two M.2 or U.2 NVME SSD hard disks.

An emergency shutdown for the input signal is provided on the mainboard directly at the ADC inputs. The emergency shutdown is intended to prevent impermissibly high signal levels from being present to the ADC and causing damage to the DSA (Digital Step Attenuator) input stage. For this purpose, an HMC536LP2E switch is built in each ADC channel. The switch is controlled separately for each channel via an RFSoC output.

The eight multiband transmit/receive modules (MTR) for the frequency range up to 6 GHz provide the necessary transmission power for the preferred band sections in the transmission direction and the required pre-amplification to achieve optimal noise behavior.

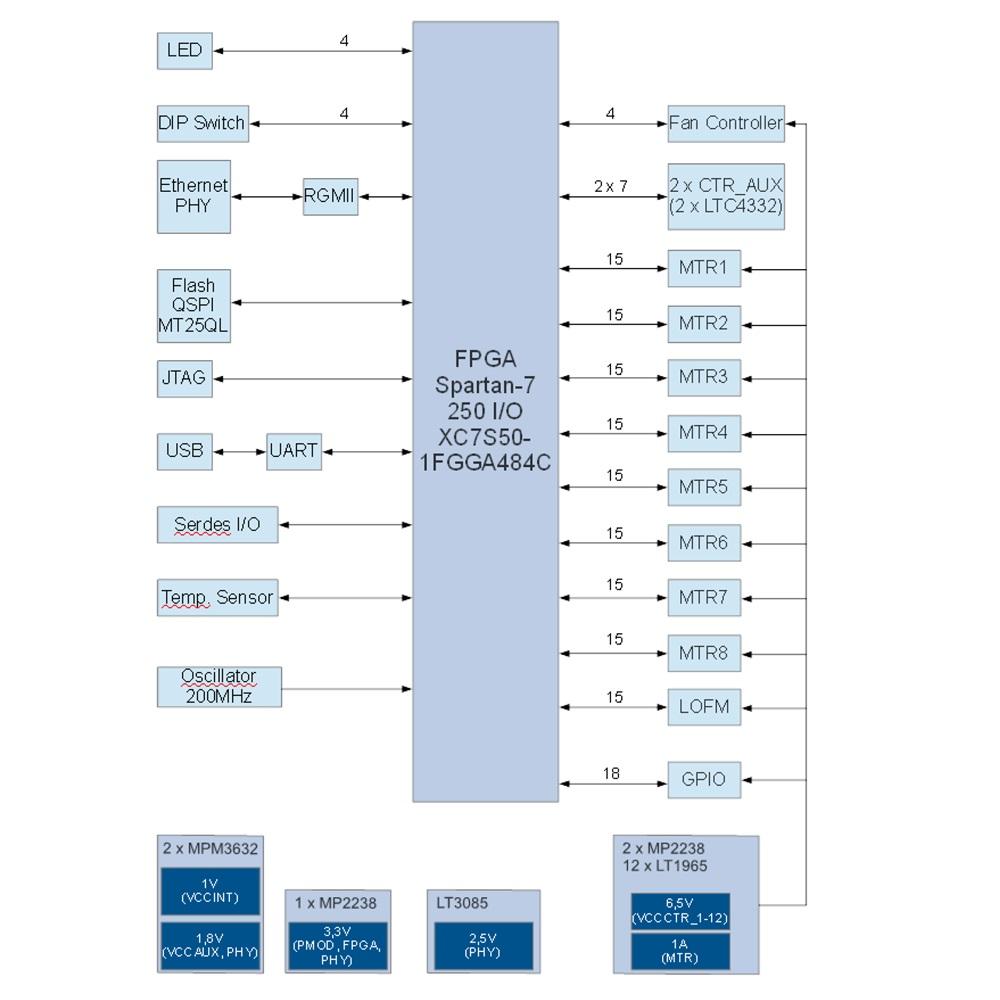

The RF control board is used to control and supply power to the MTR modules or external RF front ends. The dynamic control of the RF front ends, i.e. the setting of control parameters in the form of register contents for the individual front ends, takes place from the RFSoC. This control data is formatted on the RF control board according to the front end specific hardware interface and transmitted to the individual front end modules. The main component is a Spartan-7 FPGA, which is connected to the RFSoC via a SERDES interface. A total of 12 configurable control interfaces are available on the RF control board.

The chassis of the SDR6004 consists of individual milled aluminum parts for each wall / cover / base, which are screwed together to achieve optimum functional reliability and HF shielding effect. In addition, the MTR modules are housed in shielded milling cassettes. The RF section of the baseband assembly is also shielded (milling cassette) with a screwed cover/base to minimize interference. Heat dissipation is provided by four powerful fans mounted on a side panel, creating a transverse airflow through the case. The air inlet and outlet takes places through perforations in the side walls in the area of the fans. In order to achieve a good HF shielding effect in this area as well, the side walls were designed with a wall thickness of 12 mm. The air inlet holes are drilled with a diameter of 3 mm. The ratio of 4:1 (length/diameter) of the air inlet holes achieves a good HF shielding effect.

The basic Board Support Package of the SDR6004 includes a Xilinx Vivado Design with test routines for RFSoC and associated hardware components and interfaces, an example design ADC interface for synchronous sampling of the ADC values, an example design DAC interface for synchronous transmission of the DAC values and clock management with provision of the system-internal clocks (sample clock, processor/memory and module clock management).

ORDER NOW