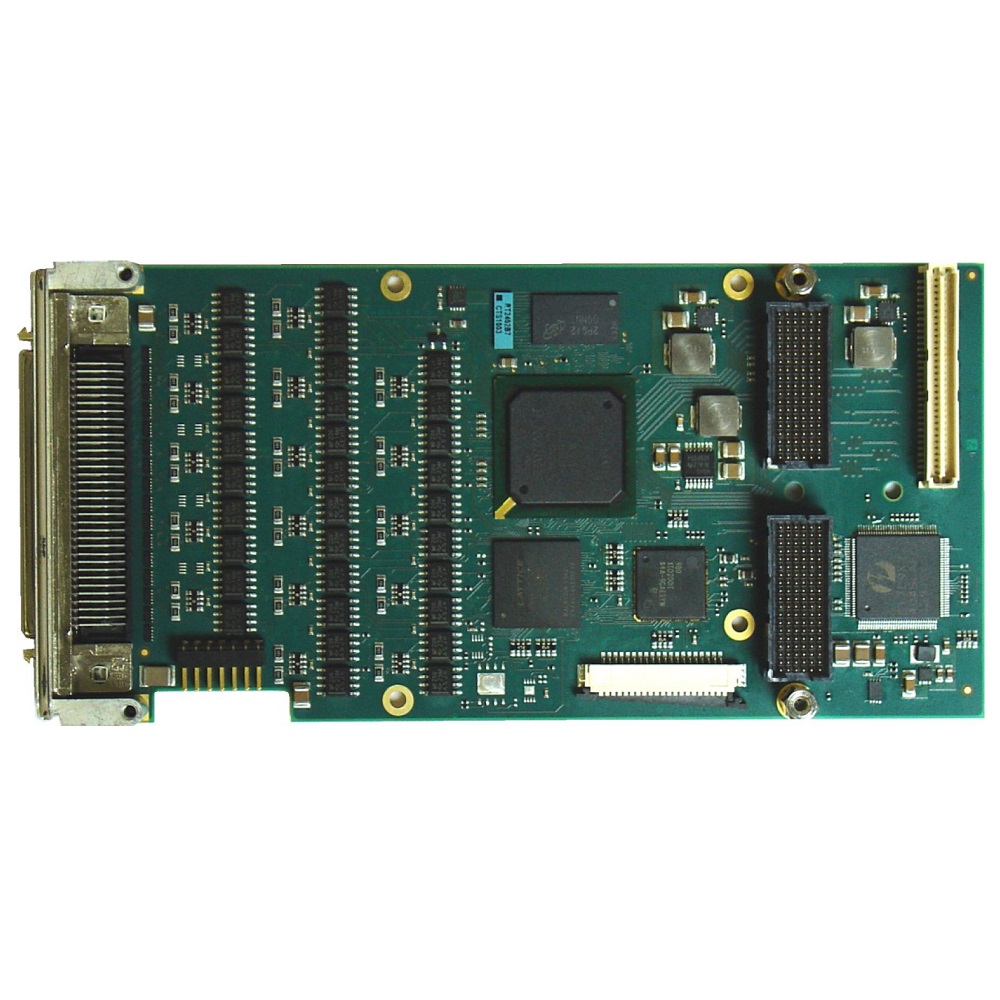

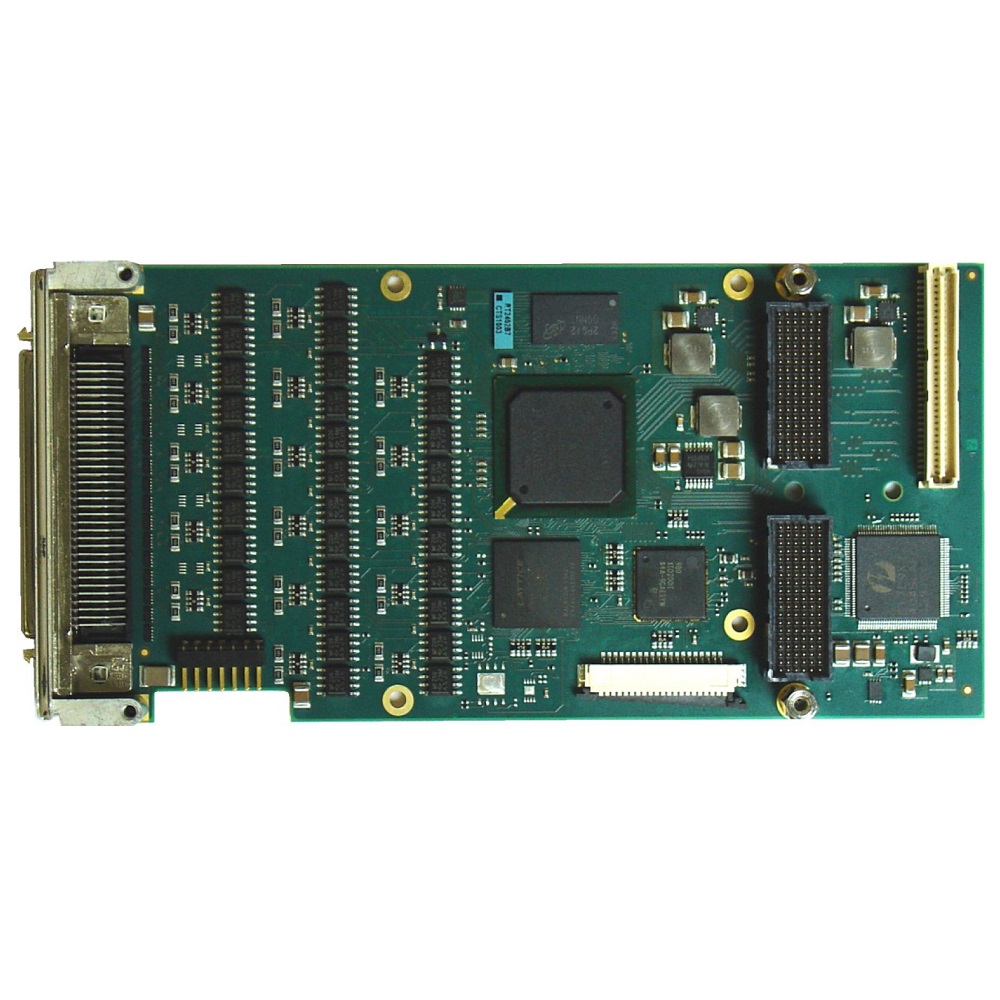

TXMC633 FPGA XMC module with 64 TTL or 32 Differential/M-LVDS I/Os

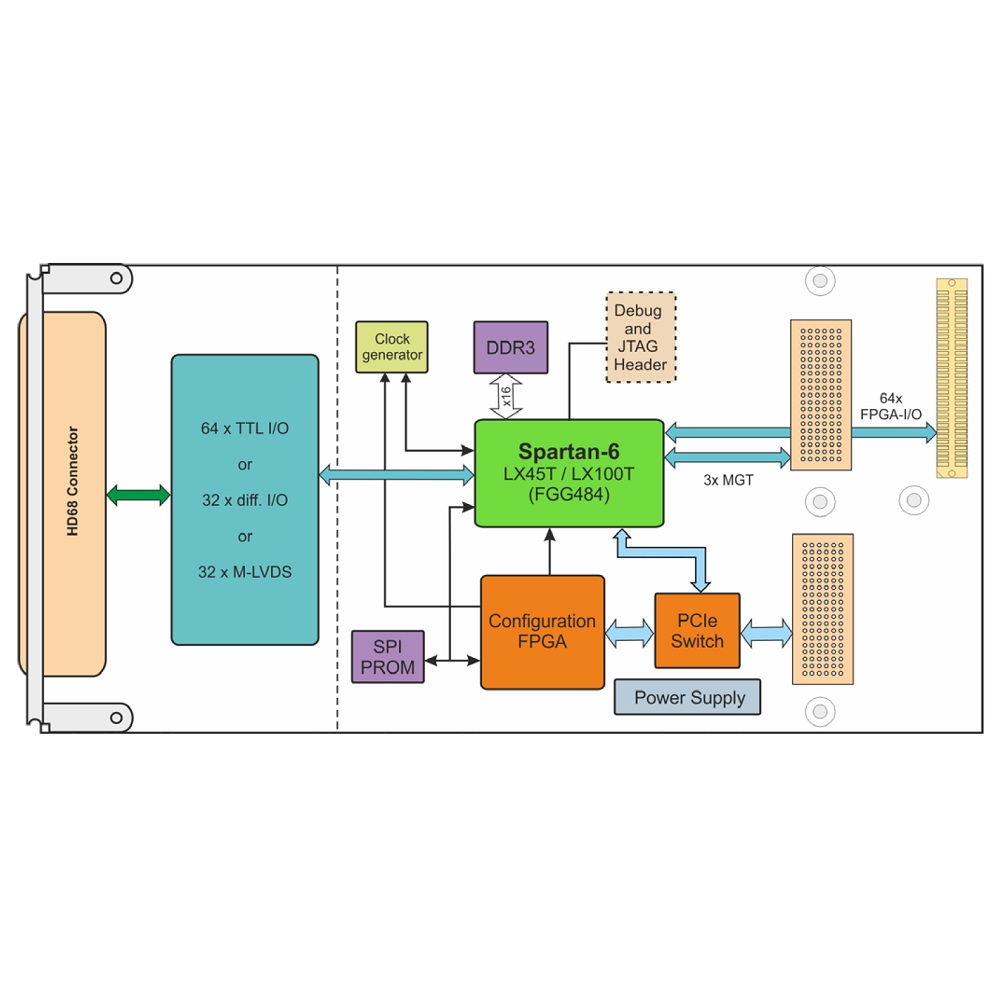

TXMC633 block diagram

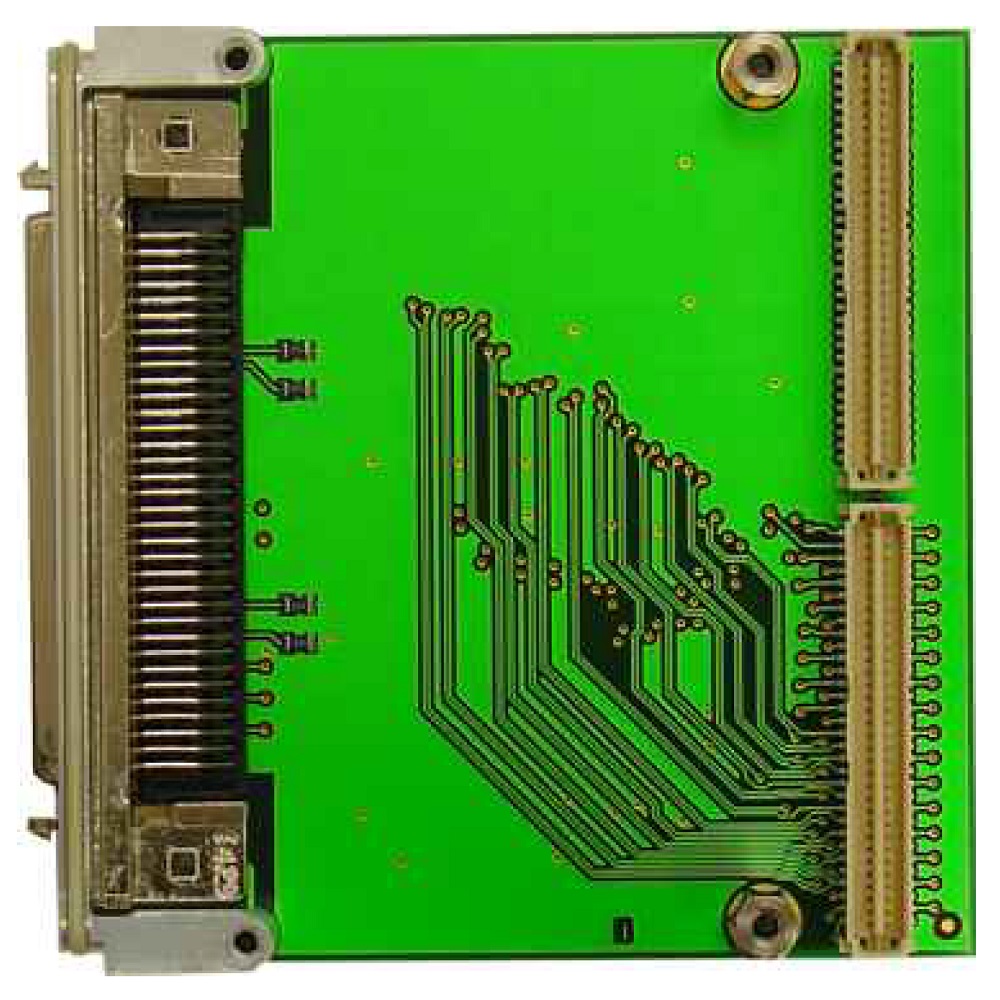

PIM module with 68 pin SCSI-3 type connector

TA104-10 1.8m cable with HD-68 connectors

TA203-10 68 pin terminal block with HD-68 connector

TA304-10 connection kit 1.8m cable with HD-68 connectors and 68 pin terminal block

TA900 program and debug box

Technical Description

- XMC module, 32 bit/33MHz PCI interface, IEEE P1386.1 compliant, PCI 2.2 compliant, 3.3V and 5V Vio

- Spartan6 FPGA: TXMC633-1x with Xilinx XC6SLX45T-2, TXMC633-2x with Xilinx XC6SLX100T-2

- Serial Flash

- 128 MB 16bit DDR3 SDRAM

- 32 Mbit SPI-EEPROM for FPGA configuration

- Flash device programmable via JTAG and in-system

- I/O lines: 64 TTL I/O (-x0R), 32 differential I/O (-x1R), 32 TTL I/O and 16 differential I/O (-x2R), 32 M-LVDS I/O (-x3R) or 32 TTL I/O and 16 M-LVDS I/O (-x4R), direction individually programmable

- TTL signaling voltage (maximum current: +/-32 mA) or EIA-422/-485 signaling level or M-LVDS standard (EIA-899)

- Front panel or P14/16 I/O

- -40°C .. +85°C operating temperature range

- Integrity, Windows, Linux, LynxOS, QNX, and VxWorks drivers available

- 5 years warranty

Order Information

TXMC633-10R

XC6SLX45T-2 FPGA XMC module with 64 TTL I/Os

TXMC633-11R

XC6SLX45T-2 FPGA XMC module with 32 differential I/Os

TXMC633-12R

XC6SLX45T-2 FPGA XMC module with 32 TTL and 16 differential I/Os

TXMC633-13R

XC6SLX45T-2 FPGA XMC module with 32 M-LVDS I/Os

TXMC633-14R

XC6SLX45T-2 FPGA XMC module with 32 TTL and 16 M-LVDS I/Os

TXMC633-20R

XC6SLX100T-2 FPGA XMC module with 64 TTL I/Os

TXMC633-21R

XC6SLX100T-2 FPGA XMC module with 32 differential I/Os

TXMC633-22R

XC6SLX100T-2 FPGA XMC module with 32 TTL and 16 differential I/Os

TXMC633-23R

XC6SLX100T-2 FPGA XMC module with 32 M-LVDS I/Os

TXMC633-24R

XC6SLX100T-2 FPGA XMC module with 32 TTL and 16 M-LVDS I/Os

TA104-10R

1.8m cable with HD-68 connectors

TA203-10R

68 pin terminal block with HD-68 connector

TA304-10R

Connection kit 1.8m cable with HD-68 connectors and 68 pin terminal block

TA900-10R

Program and debug box

TPIM003-10R

PIM module with 68 pin SCSI-3 type connector

TDRV018-SW-42

VxWorks driver

TDRV018-SW-82

LINUX driver

TXMC633-FDK

FPGA development kit